A Field Programmable Gate Array (FPGA) -based, Radiation Tolerant, Reconfigurable Computer System with Real Time Fault Detection, Avoidance, and Repair

PI: Brock LaMeres, Todd Kaiser (Co-I), Montana State University - Bozeman

PI: Brock LaMeres, Todd Kaiser (Co-I), Montana State University - Bozeman

- TA04 Robotics, Tele-Robotics and Autonomous Systems

- TA11 Modeling, Simulation, Information Technology and Processing

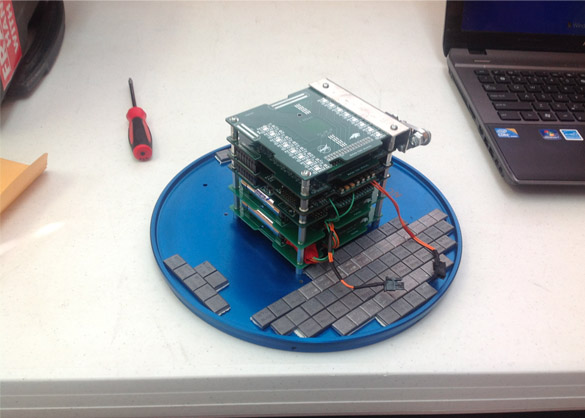

The goal is to mature the technology readiness level of the radiation tolerant, reconfigurable computer system by testing in a relevant end-to-end environment on a suborbital vehicle. To meet this goal, we need to accomplish the following objectives: (1) Implement the computer system in a form factor to meet the payload requirements of the selected suborbital vehicle; (2) Develop the power system for the payload following the requirements of the selected suborbital vehicle; and (3) Perform pre-integration testing of the system following the requirements of the selected suborbital vehicle.

Flying the system on the UP Aerospace SL-9 vehicle exceeded the original project scope. The new implementation of the computer system (in a 1U form-factor to support subsequent flight demonstrations) was able to operate for 6.5 hours on batteries and log the system counter status, the computation FPGA’s die temperature, and the G-force switch status to an SD-card while operating in a harsh temperature, vibration, acceleration, and micro-gravity environment provided by the SL-9 vehicle.

The opportunity to demonstrate the computer system on a suborbital vehicle through the Flight Opportunities Program was instrumental in maturing the technology to TRL-6. This allowed the hardware to move from a laboratory prototype to a fully functional flight unit. The computer system hardware is moving steadily toward a robust enough platform for subsequent flight demonstrations with minimal investment to achieve the next levels of TRL.

Technology Details

-

Selection DateNRA-1-APP-A (Jul 2012)

-

Program StatusCompleted

- 2 sRLV

Development Team

-

PIBrock LaMeres

-

PI Organization

-

Co-ITodd Kaiser

-

Co-I Organization

-

SponsorMontana State University, Bozeman

-

More Information